Die Kernelemente des Systems bilden der 8-Bit Mikroprozessor Z80 (U880) und dessen

Peripheriebausteine Z80-PIO (U855), Z80-CTC (U857) sowie Z80-SIO (U856). Als Anzeige

dient ein 7-Segment-LED-Display, für Eingaben ist die Tastatur mit 16 Hexadezimal-

und 9 Funktionstasten vorgesehen, der Lautsprecher ermöglicht die Wiedergabe von

Tonsignalen. Für die Kommunikation mit der Außenwelt steht eine serielle Schnittstelle

zur Verfügung und über das Tape-Interface können Programme auf Magnetband gespeichert

oder davon geladen werden. Benutzerspezifische Hardware kann am User-Bus angeschlossen

werden und am CPU-Bus sind sämtliche Adress-, Daten- und Steuerleitungen herausgeführt.

Fünf 28-polige Sockel dienen der Bestückung mit ROM-Erweiterungen, drei davon können

alternativ auch zusätzlichen RAM aufnehmen. Der Systemtakt wird von einem Quarzoszillator

mit nachgeschaltetem Frequenzteiler erzeugt.

CPU

Das Herz des LC80ex ist der Z80-Prozessor im 40-poligen DIP-Gehäuse. Es eignen sich

alle kompatiblen Varianten, die mit 5V Betriebsspannung arbeiten. Zu beachten ist,

daß die Prozessoren je nach Typ für eine bestimmte maximale Taktfrequenz ausgelegt

sind, die für stabilen Betrieb nicht überschritten werden darf. Außerdem müssen die

Peripherie-ICs (PIO/SIO/CTC) ebenfalls für die vorgesehene Taktfrequenz spezifiziert

sein. Der höchste zulässige Systemtakt richtet sich immer nach der langsamsten Einzelkomponente.

Modernere CMOS- Typen sind wesentlich sparsamer bei der Stromaufnahme (typisch 20mA),

sie brauchen nur einen Bruchteil der Energie ihrer älteren NMOS-Kollegen (typ. 200mA).

PIO

Der LC80ex ist mit zwei parallelen Ein-/Ausgabe Bausteinen vom Typ Z80-PIO ausgestattet,

die gemäß ihrer vorrangigen Bestimmung als System- bzw. User-PIO bezeichnet werden.

Aufgaben der System-PIO :

- Ansteuerung des 7-Segment-Displays (über Treiber-Transistoren)

- Abfrage der Matrixtastatur

- Ausgabe von Tonsignalen zum Lautsprecher und zum Ausgang des Tape-Interface

- Einlesen der Signale vom Eingang des Tape-Interface

Aufgaben der User-PIO:

- Port A ist vollständig auf den User-Bus herausgeführt und kann frei verwendet

werden

- die Pins 0,1,2 und 3 des Port B liegen mit Einschränkungen ebenfalls am User-Bus

an

- Pin 4,5,6 und 7 des Port B werden vom System für die Tastatur-Abfrage verwendet

Während die System-PIO vollständig für interne Prozesse benutzt wird und von außen

nicht zugänglich ist, kann über den User-Bus externe Hardware an die User-PIO angebunden

werden. Verwendungsmöglichkeiten sind bspw. Steuerungen oder das Einlesen digitaler

Signale. Port A steht dem User uneingeschränkt zur Verfügung. Am Port B werden die

Pins

4 bis 7 vom System benutzt, dies muß bei der Programmierung beachtet werden. Mehr

Details dazu im Abschnitt "User-Bus".

Bezüglich der Typenauswahl und Taktfrequenzen gilt analog das unter "CPU" gesagte.

CTC

Der Baustein Z80-CTC besitzt vier unabhängige Kanäle, die vom User für Zähler- und

Zeitgeberfunktionen programmiert werden können. Die zugehörigen Ein-/Ausgänge sind

außerdem auf den User-Bus herausgeführt. Am LC80ex können die Ausgänge ZC/TO bei

Bedarf über einen Jumper die SIO mit dem Baudratentakt versorgen.

Auch für den CTC gelten die unter "CPU" beschriebenen Bemerkungen zu Taktfrequenz

und Typ.

SIO (RS232-Interface)

Als vierte im Bunde der Z80-Familie übernimmt die Z80-SIO die serielle Kommunikation

mit der Außenwelt. Diese Komponente wurde beim LC80ex nachgerüstet, sie existiert

nicht in den Urversionen des LC80. Die SIO hat zwei Kanäle, welche zum komfortablen

Datenaustausch mit anderen Geräten nutzbar sind. Praktische Anwendungen sind bspw.

das schnelle Laden und Speichern von Programmen am PC oder eine Schnittstelle zu

Terminalprogrammen.

Port B ist zu diesem Zweck bereits über einen MAX232 auf eine Sub-D-Buchse verlegt

und kann über Jumper JP12 den Baudratentakt vom CTC beziehen. Zudem sind die Anschlüsse

beider Ports auf Stiftleisten herausgeführt, sodaß mit Hilfe von Zusatzhardware auch

Port A verfügbar wird.

Achtung!

Aufgrund des verwendeten Pinouts sind für den LC80ex nur SIO-ICs vom Typ Z80-SIO/0

oder kompatible (z.B. U856) geeignet! Andere Versionen funktionieren wegen abweichender

Pinbelegung nicht!

Wie bei CPU, PIO und CTC muß außerdem die für den Typ maximal zulässige Taktfrequenz

beachtet werden.

RAM-Bänke

Der klassische Arbeitsspeicher des LC80 besteht aus aus 8 Steckplätzen für 2114-kompatible

SRAMs, von denen jeweils zwei zu einer Bank gehören. Der 2114 besitzt eine Kapazität

von 1KB bei 4 Bit Breite, daher müssen immer zwei paarweise bestückt werden. Die

RAM-Bänke werden bei gesetztem Jumper JP7 im Speicherbereich 2000-2FFFH angesprochen.

Sie können jedoch bei Bedarf durch Öffnen von JP7 deaktiviert und die Basisadresse

2000H anderweitig zugewiesen werden. Dies macht bspw. Sinn, wenn der RAM alternativ

auf den Sockeln 3-5 bestückt werden soll. Siehe dazu die Erklärungen im Abschnitt

Speicherbestückung.

ROM/RAM Sockel

Für die Aufnahme von EPROMs stehen fünf 28-polige Sockel zur Verfügung. Die Steckplätze

3 bis 5 können alternativ auch mit SRAM bestückt und mittels der Jumper JP2/JP3/JP4

entsprechend konfiguriert werden. Die Zuordnung der Basisadressen ist frei wählbar.

Details zu den geeigneten Speichertypen sowie den zugehörigen Einstellungen werden

in den Abschnitten Speicherbestückung und Jumper beschrieben.

Desweiteren ist es möglich, den Inhalt eines auf Sockel 5 gesteckten SRAMs bei fehlender

Stromversorgung über eine Stützbatterie zu erhalten (siehe "Batteriebackup").

Adressdecoder

Die Logik des Adressdecoders sorgt dafür, daß beim Ansprechen einer Speicheradresse

der zugehörige physische RAM- bzw. ROM-IC aktiviert wird. Die Regel "Es kann nur

einen geben!" gilt nicht nur für den Highlander, sondern trifft auch auf den Datenbus

eines Rechners zu. Würden sich mehrere Speicherbausteine gleichzeitig an den Bus

schalten, gäbe es erstens Datensalat und zweitens könnten sich die Ausgangstreiber

der ICs gegenseitig zerstören. Im Ruhezustand (nicht selektiert) sind die Datenpins

D0-D7 daher hochohmig. Sobald der Adressdecoder den Speicher-IC auswählt, indem er

dessen Chipselect-Eingang auf LOW zieht, werden die Datenpins aktiv und die CPU kann

die von den Adressleitungen gewählte Speicherzelle lesen bzw. schreiben.

Der Adressdecoder des LC80ex besteht aus den ICs AD1 bis AD4 und hat 16 Ausgänge

(0-F). Demzufolge kann er die Adressen in Bereiche zu je 4KB auflösen. Die erste

Adresse jedes Bereiches heißt "Basisadresse", z.B. ist 0000H die Basisadresse des

Bereiches 0000-0FFFH, 1000H die des Bereiches 1000-1FFFH und so weiter. Die mit den

Basisadressen korrespondierenden Decoderausgänge sind mit Ausnahme von "2", "9" und

"A" auf den Jumper JP6 herausgeführt und können dort den gewünschten Chipselect-Leitungen

der Sockel 1-5 frei zugeordnet werden. Die Decoderausgänge "9" und "A" lassen sich

bei Bedarf direkt am IC AD3 abgreifen (Stiftleiste). Eine Besonderheit stellt der

Ausgang "2" dar, denn er ist im Normalfall über JP7 den RAM-Bänken zugordnet, wie

es der Konfiguration des Ur-LC80 entspricht. Wenn es die Umstände erfordern, kann

JP7 aber auch geöffnet werden, sodaß die Basisadresse 2000H anderweitig zur Verfügung

steht.

Desweiteren besitzt der Adressdecoder speziell für die RAM-Bänke 1-4 (2114) eine

zusätzliche Logik, die in Schritten von 1K auflöst, damit die jeweils 1KB großen

Bänke korrekt selektiert werden.

Ich habe auf Basis des Logik-Simulators Logisim ein interaktives Modell erstellt,

mit dem die Funktionsweise des Adressdecoders anschaulich nachvollzogen werden kann.

Siehe Downloads/Sonstiges oder hier klicken.

Taktgenerator

Der Taktgenerator erzeugt den für das System unentbehrlichen Herzschlag. Die Oszillator-Schaltung

ist einfach aufgebaut und besteht neben dem Quarz nur aus zwei Inverter-Gattern,

zwei Widerständen und einem Kondensator. Nachgeschaltete D-Flipflops teilen den Takt

auf die Hälfte und ein Viertel der Quarzfrequenz herunter. Die Ausgänge des Taktgenerators

sind auf den Jumper JP9 geführt, über den das passende Teilerverhältnis eingestellt

wird. Für den Betrieb der SIO empfiehlt sich der Einsatz eines Baudraten-Quarzes.

Am tauglichsten ist die Frequenz 3,6864MHz. Auf ein Viertel geteilt ergeben sich

ca. 922KHz, was in etwa der Taktfrequenz von 900KHz des Ur-LC80 entspricht . Das

Magnetbandinterface hat mit dieser leichten Abweichung keine Probleme, seinerzeit

mit dem originalen LC80 auf Band gesicherte Programme ließen sich einwandfrei einlesen.

Die Bestückung der ICs CG1 und CG2 ist hingegen leicht kritisch. Nicht jede Kombination

aus Inverter und D-Flipflop arbeitet stabil. Schmitt-Trigger Inverter wie der 74LS14

(DL014) haben sich im praktischen Versuch als untauglich erwiesen. Das Taktsignal

ist unsauber und verursacht wegen Überschwingern Fehlfunktionen beim nachgeschalteten

Frequenzteiler. Normale Inverter (74LS04 bzw. DL004) funktionieren dagegen gut (siehe

auch Diskussions-Thread ab Posting #165).

Bei Bedarf kann der Taktgenerator mit einer separaten Sandwichplatine realisiert

werden, entsprechende Anschlüsse und mechanische Stützpunkte sind vorbereitet.

Tape-Interface / Lautsprecher

Das Tape-Interface hat die Aufgabe, Programme auf Magnetband zu speichern oder davon

einzulesen. Es ist für den in der DDR üblichen Pegel von 100mV ausgelegt. Der Sendeteil

wurde unverändert vom LC80 übernommen. RC-Glieder bedämpfen vor der DIN-Buchse das

von der System-PIO ausgegebene Rechtecksignal, welches über T16 auch den Lautsprecher

und die OUT-LED ansteuert. Als Lautsprecher ist im originalen LC80 eine HS77 Telefonkapsel

verbaut, die jedoch unproblematisch durch andere Schallgeber, z.B. Klein- oder Piezolautsprecher,

ersetzt werden kann. Die Lautstärke läßt sich in gewissen Grenzen mit dem Auskoppelkondensator

C44 beeinflussen.

Ab Platinenversion V3 gibt es zusätzlich eine Transistorstufe mit vorgeschaltetem

Trimmpoti zur Verstärkung des Signals, um die Lautstärke anzuheben bzw. nach Bedarf

einstellen zu können. Mit dem ebenfalls hinzugekommenen Jumper JP14 "Mute" kann der

Lautsprecher schnell stummgeschaltet werden.

Der Empfangsteil wurde für den LC80ex komplett neu entworfen. Anstelle des B761,

der aufgrund seiner 6-poligen Bauform und seiner Eigenschaft als Open-Collector Typ

mittlerweile recht exotisch ausfällt, kommt ein gut verfügbarer Dual-OPV im DIP-8

Gehäuse zum Einsatz. Der 100k-Widerstand R45 am Eingang soll hochohmige Einstreuungen

unterdrücken. Die erste Stufe des OPV arbeitet als Bandpaß und bevorzugt das interessante

Spektrum um 1 bis 2kHz. Bei sehr pegelschwachen Quellen kann die Verstärkung ggfs.

durch einen größeren Wert für R46 erhöht werden. Die zweite Stufe ist als Schmitt-Trigger

geschaltet und formt das Signal zu einem sauberen Rechteck, bevor es an die System-PIO

geleitet wird. Da für die Stromversorgung lediglich einseitige 5V zur Verfügung stehen,

eignen sich als OPV nur für Single-Supply ausgelegte Typen, möglichst Rail2Rail.

Im Testaufbau lieferten AD822 und LT1078 die saubersten Signale, in der Praxis tut

es aber auch der wesentlich preiswertere LM358.

Netzteil

Um Platz für die Nachrüstung der SIO zu schaffen, mußte ich das Netzteil gegenüber

dem Original wesentlich gedrängter aufbauen. Ermöglicht wurde dies durch einen Inline-Graetzgleichrichter

anstelle der diskreten Dioden, eine kleinere Eingangsbuchse, stehende Montage der

Ladeelkos und Entstörspulen sowie einen platzsparenden, aber dennoch effektiven Kühlkörper

und den Verzicht auf Bestückungsmöglichkeiten für Spannungsregler im TO-3 Gehäuse.

Die Schaltung bedarf kaum der Erklärung. Die Eingangsspannung passiert zunächst den

Entstörfilter aus L1/L2/C47 sowie den Brückengleichrichter und wird anschließend

vom Längsregler 7805 auf 5V konstant gehalten. Die Supressor-Diode Z1 soll die Platine

vor Überspannungsspitzen schützen.

Das Netzteil kann sowohl mit Gleich- als auch Wechselspannung betrieben werden. Es

ist für einen Maximalstrom von 1 Ampere ausgelegt. Im Normalfall genügt das auch

bei Bestückung mit stromhungrigen NMOS-ICs. Sollte jedoch am User- oder CPU-Bus betriebene

Peripherie über den LC80ex versorgt werden, muß darauf geachtet werden, daß der Maximalstrom

nicht überschritten wird. Im Hinblick auf die vom Kühlkörper abzuführende Verlustleistung

ist dies besonders wichtig, wenn gleichzeitig mit hoher Eingangsspannung gearbeitet

wird. Diese sollte nicht höher als 9V AC bzw. 12V DC sein. Die Untergrenze wird vom

Typ des Längsreglers bestimmt und liegt bei Bestückung mit einem Standard 7805 um

die 7V AC bzw. 9V DC. Bitte beachten, daß alternativ zum 7805 verbaute Low-Drop Typen

eventuell größere Abblock-Kondensatoren (C25/C26) benötigen.

Dem Anwender steht es natürlich frei, die gesamte Netzteilschaltung wegzulassen und

stattdessen extern stabilisierte 5V einzuspeisen. Dazu muß lediglich eine Drahtbrücke

vom Mittenkontakt der Buchse zur Plusschiene eingelötet werden.

Ab Platinenversion V3 sind direkt neben der Buchse Lötaugen für einen optionalen

Schalter vorhanden, damit die Stromzufuhr ohne Ziehen des Kabels unterbrochen werden

kann. Das ist bspw. für "kalten Reset" nützlich.

An dieser Stelle ein Hinweis. Wackelkontakte in der Stromversorgung können CMOS-ICs

durch Latchup-Effekte zerstören! Alle aktuell hergestellten Z80-Komponenten sowie

Speicher sind in der Regel CMOS-Typen. Ich empfehle daher, nur zuverlässige Netzteile

zu verwenden und besonderes Augenmerk auf die Verbindung Stecker/Buchse zu legen.

So passen bspw. Stecker der Dimension 5,5/2,5mm auch in die am LC80ex verwendete

Buchse 5,5/2,1mm, haben aber keinen sicheren Kontakt.

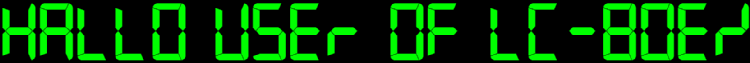

Display

Das Display besteht aus drei zweistelligen 7-Segment-Anzeigen vom Typ VQE23, die

per Multiplex angesteuert werden. Port A der System-PIO schaltet über die Transistoren

T7-T14 die Segmente und den Dezimalpunkt, während Port B mit Hilfe von T1-T6 die

gewünschte Stelle aktiviert. Die Anoden gleichwertiger Segmente hängen zusammen an

jeweils einem der "Zeilentreiber" T7-T14, während jede Kathode ihren eigenen "Spaltentreiber"

besitzt (T1-T6). Mit dieser Beschaltung ist es möglich, daß alle Segmente einer Stelle

gemeinsam leuchten. Es darf jedoch immer nur eine Stelle aktiv sein, weil die Transistoren

T7-T14 nicht für den Strom mehrerer Segmente ausgelegt sind und überlastet werden

könnten. Darauf muß bei der Programmierung eigener Anzeigeroutinen geachtet werden.

Außerdem gilt es zu berücksichtigen, daß Port B auch für die Abfrage der Tastatur

mit zuständig ist und daher die Leitungen der Bits PB2 bis PB7 dort ebenfalls anliegen.

Tastatur

Am originalen LC80 kam eine modifizierte Taschenrechner-Tastatur zum Einsatz, die

mit der Platine fest verlötet war. Das Keyboard des LC80ex besteht zwecks einfachem

Nachbau aus einer einlagigen Platine, die mit handelsüblichen SMD-Mikroschaltern

bestückbar ist und per Stiftleiste auf die Hauptplatine gesteckt wird. Die Zeichnungen

des Layouts, der Bohrplan für die Deckplatte sowie die Beschriftungsvorlage sind

unter DOWNLOADS/PDF-Doku zu finden. Zum Öffnen und Drucken der Sprintlayout-Dateien

kann der kostenlos von Abacom bereitgestellte Viewer benutzt werden. Stiftleistenbelegung

und Matrix-Schema finden sich im Schaltplan.

Die 16 Hexadezimal- und 7 Funktionstasten sind als Matrix verschaltet. Deren Abfrage

erfolgt in Kooperation von System- und User-PIO. Die Tasten "RESET" und "NMI" gehören

nicht zur Matrix, sondern werden von Invertern des IC CG1 gepuffert und wirken danach

direkt auf die entsprechenden Pins der CPU. Zusätzlich sorgt eine aus zwei Gattern

des IC AD2 bestehende RESET-Logik für das korrekte Rücksetzen der Peripherie-Bausteine

(PIO, SIO, CTC).

Batteriebackup

Sofern der Sockel Nr.5 mit einem SRAM bestückt ist, kann dessen Inhalt bei Abschalten

oder Ausfall der Stromversorgung mit einer Batterie gepuffert werden. Die Batterie

ist in Form einer CR2032 Knopfzelle im dafür vorgesehenen Halter bestückbar (Achtung!

Unbedingt Hinweise unter Errata lesen!) oder wird alternativ am Jumper JP1 angeschlossen.

Die Entkopplungsdioden müssen Typen mit möglichst niedriger Flußspannung sein, um

den Spannungsabfall gering zu halten. Siehe auch Bestückungshinweise.

User-Bus

Zum Anschluß externer Peripherie sind die Ports der User-PIO und der CTC auf den

User-Bus herausgeführt. Alle Funktionen der CTC, Port A der User-PIO sowie die Steuerleitungen

ASTB, BSTB, ARDY und BRDY stehen vollständig zur Verfügung. Von Port B der User-PIO

sind nur die Pins PB0 bis PB3 nutzbar, weil PB4 bis PB7 intern zur Abfrage der Tastatur-Matrix

dienen. Dies muß auch programmtechnisch berücksichtigt werden, sofern Port B für

eigene Funktionen zur Anwendung kommt.

Unter Beachtung der zulässigen Gesamtstromaufnahme von 1 Ampere kann angeschlossene

Peripherie aus dem Netzteil des LC80ex versorgt werden, die 5V-Schiene liegt am Connector

an. Details zur Anschlußbelegung der Steckverbinder verrät der Schaltplan. Der User-Bus

des LC80ex ist 100% kompatibel zu dem des originalen LC80.

CPU-Bus

Der CPU-Bus ist für Hardware-Erweiterungen vorgesehen. Hier liegen sämtliche Adress-,

Daten-, und Steuerleitungen der CPU an. Außerdem kann der interne Speicher (RAM und

ROM) komplett deaktiviert werden, indem der Anschluß MEDI (Memory Disable) auf "LOW"

gezogen wird. Auch am CPU-Bus liegen die internen 5V an, um Erweiterungen zu versorgen.

Die vollständige Anschlußbelegung ist im Schaltplan dokumentiert.

Achtung, der CPU-Bus des LC80ex ist NICHT mit dem des originalen LC80 kompatibel!

Aus layouttechnischen Gründen weicht die Belegung der Steckverbinder zum Teil ab.